2022. 2. 7. 15:15ㆍMajor`/컴퓨터구조

제어 유니트 (Control Unit)

CPU에서 명령어를 인출하여 해독하고 실행하는 과정이 순차적으로 발생하기 위해서 순간마다 적절한 제어 신호를 생성해서 해당 하드웨어 모듈로 보내주는 장치

- 기능 1) 명령어 코드의 해독

- 기능 2) 명령어 실행에 필요한 제어 신호 생성

≫ 명령어 사이클이 적절히 수행되도록 모든 동작들을 제어하는 장치

- 명령어 사이클에는 인출 사이클/간접 사이클/실행 사이클/인터럽트 사이클로 구성

- 각 사이클에는 여러 개의 마이크로-연산들이 수행된다

Example) 인출 사이클

t(0) : PC -> MAR

t(1) : M[MAR] -> MBR / PC + 1 -> PC

t(2) : MBR -> IR- t(1)에서는 두 개의 마이크로-연산이 동시에 수행된다

- 각 마이크로-연산들이 실제로 수행되려면 2진 비트들로 표현되어야 한다

- 비트들로 이루어진 각 단어 : 마이크로 명령어(Microinstruction)/제어 단어(Control Word)

- 마이크로 명령어들의 집합 : 마이크로프로그램(Microprogram)

- CPU의 특정 기능을 수행하기 위해 마이크로프로그램을 논리적으로 묶은 그룹 : 루틴(Routine)

- 명령어 실행을 하나의 마이크로프로그램이라고 생각해보면

- 해당 마이크로프로그램은 3개의 루틴으로 구성되어 있다 :: 인출 사이클 루틴/간접 사이클 루틴/실행 사이클 루틴

제어 유니트의 내부구조

명령어 레지스터 (IR : Instruction Register)

- 현재 실행중인 명령어를 저장하고 있는 레지스터

명령어 해독기 (ID : Instruction Decoder)

- IR로부터 들어오는 명령어의 opcode를 해독

- 해당 연산을 수행하기 위한 루틴의 시작 주소를 결정 :: 사상(Mapping) 방식

- 사상 방식을 통해서 결정된 주소는 CAR에 저장된다

※ 사상 함수 사용 이유

- 명령어가 수행될 때, 주기억장치에 접근하려면 명령어의 Operand를 주기억장치에 직접 적용될 수 있는 Operand로 변환해야 하기 때문이다

제어 주소 레지스터 (CAR : Control Address Register)

- 다음에 실행할 마이크로명령어의 주소를 저장하는 레지스터

- → 해당 주소는 제어 기억장치의 특정 위치를 가리킨다

제어 기억장치 (CM : Control Memory)

- 마이크로프로그램을 저장하는 내부 기억장치

- ROM으로 만든다

Example) 용량이 128 word인 제어 기억장치

| 0 | 인출 사이클 루틴 |

| .... | 간접 사이클 루틴 |

| ..... | 인터럽트 사이클 루틴 |

| .... | |

| 63 | |

| 64 | 실행 사이클 루틴 1 |

| ... | 실행 사이클 루틴 2 |

| .... | |

| .... | |

| 127 |

- 0 ~ 63 (64 word) : 공통 루틴(인출/간접/인터럽트)을 위한 마이크로프로그램 루틴들을 저장

- 64 ~ 127 (64 word) : 각 명령어를 위한 실행 사이클 루틴들을 저장

제어 버퍼 레지스터 (CBR : Control Buffer Register)

- 제어 기억장치로부터 읽힌 마이크로명령어를 일시적으로 저장하는 레지스터

서브 루틴 레지스터 (SBR : Subroutine Register)

- 마이크로프로그램에서 서브루틴이 호출되는 경우에, 현재 CAR 내용을 일시적으로 저장하는 레지스터

순서 제어 모듈 (SM : Sequencing Module)

- 마이크로명령어의 실행 순서를 결정하는 회로들의 집합

CPU의 명령어 셋 설계

1. 명령어들의 종류/비트 패턴을 정의

2. 해당 명령어들의 실행에 필요한 하드웨어를 설계

3. 각 명령어를 위한 실행 사이클 루틴을 마이크로프로그래밍

- 마이크로프로그램은 루틴들의 집합이므로 CPU 설계 단계에서 확정되고, 변하지 않는다

- 제어 기억장치는 ROM으로 만들어져서 CPU 칩 내에 포함된다

사상 함수 생성 방법

(1) 제어 기억장치의 용량이 2w라면

- 사상 함수 전체 길이 = w

(2) 각 루틴이 최대 n개의 마이크로명령어로 구성된다면

- 2k = n을 만족하는 k에 대해서

- 사상 함수 끝 k자리를 0으로 만들어준다

(3) 실행 사이클이 처음~절반 or 절반~끝

- 처음~절반 : 사상 함수 첫번째 자리를 0

- 절반~끝 : 사상 함수 첫번째 자리를 1

(4) (2), (3) 방법을 통해 구현하고, 사상 함수의 남은 자리를 X로 채워준다

Example 1) 사상함수 생성

:: 제어 기억장치 용량이 1024이고, 각 루틴이 최대 16개의 마이크로명령어로 구성되고, 처음-절반 부분에 실행 사이클 루틴들을 저장

(1) 용량이 1024 = 210이므로 사상 함수 전체 길이 = 10

(2) 각 루틴이 최대 24개의 마이크로명령어 구성 → 사상 함수 끝 4자리를 0으로 만들어준다

| 0 | 0 | 0 | 0 |

(3) 처음-절반 부분에 실행 사이클 루틴들을 저장 → 사상 함수 첫번째 자리를 0으로 설정

| 0 | 0 | 0 | 0 | 0 |

(4) 나머지 자리를 X로 채워준다

| 0 | X | X | X | X | X | 0 | 0 | 0 | 0 |

- 최종 사상 함수 : 0 XXXXX 0000

Example 2) 사상함수 생성

:: 제어 기억장치 용량이 512이고, 각 루틴이 최대 8개의 마이크로명령어로 구성되고, 절반-끝 부분에 실행 사이클 루틴들을 저장

(1) 용량이 512 = 29이므로 사상 함수 전체 길이 = 9

(2) 각 루틴이 최대 23개의 마이크로명령어 구성 → 사상 함수 끝 3자리를 0으로 만들어준다

| 0 | 0 | 0 |

(3) 절반-끝 부분에 실행 사이클 루틴들을 저장 → 사상 함수 첫번째 자리를 1으로 설정

| 1 | 0 | 0 | 0 |

(4) 나머지 자리를 X로 채워준다

| 1 | X | X | X | X | X | 0 | 0 | 0 |

- 최종 사상 함수 : 1 XXXXX 000

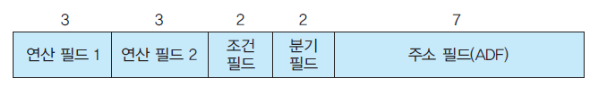

마이크로명령어의 형식

연산 필드

- 연산 필드의 개수만큼 마이크로-연산을 동시에 수행할 수 있다

조건 필드(CD)

- 분기에 사용될 조건 플래그를 지정한다 (if, switch문과 같은 조건문)

분기 필드(BR)

- 분기의 종류, 다음에 실행할 마이크로명령어의 주소를 결정하는 방법을 명시한다

주소 필드(ADF)

- 분기가 발생하는 경우, 목적지 마이크로명령어의 주소로 사용한다

Ex) 연산 필드1 마이크로-연산

| 코드 | 마이크로-연산 | 기호 |

| 000 | None | NOP |

| 001 | PC → MAR | PCTAR |

| 010 | IR(addr) → MAR | IRTAR |

| 011 | AC + MBR → AC | ADD |

| 100 | M[MAR] → MBR | READ |

| 101 | MBR → AC | BRTAC |

| 110 | MBR → IR | BRTIR |

| 111 | MBR → M[MAR] | WRITE |

Ex) 연산 필드2 마이크로-연산

| 코드 | 마이크로-연산 | 기호 |

| 000 | None | NOP |

| 001 | PC + 1 → PC | INCPC |

| 010 | AC → MBR | ACTBR |

| 011 | PC → MBR | PCTBR |

| 100 | MBR → PC | BRTPC |

| 101 | SP → MAR | SPTAR |

| 110 | AC - MBR → AC | SUB |

| 111 | IR(addr) → PC | IRTPC |

Ex) 조건 필드 코드 지정

| 코드 | 조건 | 기호 | 설명 |

| 00 | 1 | U | 무조건 분기 |

| 01 | I 비트 | I | 간접 주소지정 >>I비트가 1이면 간접 사이클 루틴 호출 |

| 10 | AC(S) | S | 누산기에 저장된 데이터의 부호 >> S플래그가 1(=음수)이면 분기 |

| 11 | AC=0 | Z | AC에 저장된 데이터가 0 >> Z플래그가 1(=데이터가 0)이면 분기 |

Ex) 분기 필드 코드 지정

| 코드 | 기호 | 설명 |

| 00 | JMP | 1) 조건필드에 의해 분기가 일어나면 >> ADF → CAR (해당 마이크로명령어로 점프) ------------------------------------------------------------------------------------------- 2) 조건필드에 의해 분기가 일어나지 않으면 >> CAR + 1 → CAR (다음 마이크로명령어 실행) |

| 01 | CALL | 1) 조건필드에 의해 분기가 일어나면 >> CAR + 1 → SBR / ADF → CAR (다음 마이크로명령어를 SBR에 저장해놓고, 해당 마이크로명령어로 점프) ------------------------------------------------------------------------------------------- 2) 조건필드에 의해 분기가 일어나지 않으면 >> CAR + 1 → CAR (다음 마이크로명령어 실행) |

| 10 | RET | SBR → CAR >> 서브루틴으로부터 복귀 |

| 11 | MAP | 사상 방식을 통해 결정된 주소를 CAR에 저장 ※ IF 1 XXXX 00 >> CAR(1) ← 1 / CAR(2-5) ← IR(op) / CAR(6,7) ← 0 |

| 0 | 인출 사이클 루틴 |

| 4 | 간접 사이클 루틴 |

| 8 | 인터럽트 사이클 루틴 |

| .... | |

| 63 | |

| 64 | 실행 사이클 루틴 1 (NOP) |

| 68 | 실행 사이클 루틴 2 (LOAD) |

| 72 | 실행 사이클 루틴 3 (STORE) |

| 76 | 실행 사이클 루틴 4 (ADD) |

| 80 | 실행 사이클 루틴 5 (SUB) |

| 84 | 실행 사이클 루틴 6 (JUMP) |

| .... | |

| 127 |

1) 인출 사이클 루틴

t(0) : PC -> MAR

t(1) : M[MAR] -> MBR / PC + 1 -> PC

t(2) : MBR -> IR| ORG 0 (시작 주소 0) |

| 연산 기호 | 조건 기호 | 분기 기호 | 분기 목적지 | 설명 | |

| FETCH: | PCTAR | U | JMP | NEXT | ; PC → MAR ; 다음 마이크로명령어 실행 |

| READ, INCPC | U | JMP | NEXT | ; M[MAR] → MBR ; PC + 1 → PC ; 다음 마이크로명령어 실행 |

|

| BRTIR | U | MAP | ; MBR → IR, 해당 명령어 실행 ; 매핑을 통해서 CAR에 해당 명령어의 실행 사이클 루틴 시작 주소 적재 |

>> 마이크로명령어들을 2진 비트 패턴으로 변환

| 주소 | 마이크로-연산 필드 | 조건 필드(CD) | 분기 필드(BR) | 주소 필드(ADF) |

| 000 0000 | 001 000 | 00 | 00 | 000 0001 |

| 000 0001 | 100 001 | 00 | 00 | 000 0010 |

| 000 0010 | 110 000 | 00 | 11 | ? |

2) 간접 사이클 루틴

t(0) : IR(addr) -> MAR

t(1) : M[MAR] -> MBR

t(2) : MBR -> IR(addr)| ORG 4 (시작 주소 4) |

| 연산 기호 | 조건 기호 | 분기 기호 | 분기 목적지 | 설명 | |

| INDRT: | IRTAR | U | JMP | NEXT | ; IR(addr) → MAR ; 다음 마이크로명령어 실행 |

| READ | U | JMP | NEXT | ; M[MAR] → MBR ; 다음 마이크로명령어 실행 |

|

| BRTIR | U | RET | ; MBR → IR(addr) ; 실행 사이클 루틴으로 복귀 |

>> 마이크로명령어들을 2진 비트 패턴으로 변환

| 주소 | 마이크로-연산 필드 | 조건 필드(CD) | 분기 필드(BR) | 주소 필드(ADF) |

| 000 0100 | 010 000 | 00 | 00 | 000 0101 |

| 000 0101 | 100 000 | 00 | 00 | 000 0110 |

| 000 0110 | 110 000 | 00 | 10 | 000 0000 |

3) 실행 사이클 루틴

| 명령어 | 연산 코드 | 루틴의 시작 주소 (사상 함수 적용) >> 사상 함수 : 1 XXXX 00 |

| NOP | 0000 | 1 0000 00 = 64 |

| LOAD(I) : 간접 주소 지정 |

0001 | 1 0001 00 = 68 |

| STORE(I) : 간접 주소 지정 |

0010 | 1 0010 00 = 72 |

| ADD | 0011 | 1 0011 00 = 76 |

| SUB | 0100 | 1 0100 00 = 80 |

| JUMP | 0101 | 1 0101 00 = 84 |

NOP

t(0) : PC + 1 -> PC| ORG 64 (시작 주소 64) |

| 연산 기호 | 조건 기호 | 분기 기호 | 분기 목적지 | 설명 | |

| NOP: | INCPC | U | JMP | FETCH | ; PC + 1 -> PC ; 인출 사이클 루틴으로 복귀 |

>> 마이크로명령어들을 2진 비트 패턴으로 변환

| 주소 | 마이크로-연산 필드 | 조건 필드(CD) | 분기 필드(BR) | 주소 필드(ADF) |

| 1 0000 00 | 000 001 | 00 | 00 | 0000 000 |

LOAD(I)

t(0) : IR(addr) -> MAR

t(1) : M[MAR] -> MBR

t(2) : MBR -> AC| ORG 68 (시작 주소 68) |

| 연산 기호 | 조건 기호 | 분기 기호 | 분기 목적지 | 설명 | |

| LOAD(I): | NOP | I | CALL | INDRT | ; I=1 : 간접 사이클 루틴 호출 |

| IRTAR | U | JMP | NEXT | ; IR(addr) -> MAR ; 다음 마이크로명령어 실행 |

|

| READ | U | JMP | NEXT | ; M[MAR] -> MBR ; 다음 마이크로명령어 실행 |

|

| BRTAC | U | JMP | FETCH | ; MBR -> AC ; 인출 사이클 루틴으로 복귀 |

>> 마이크로명령어들을 2진 비트 패턴으로 변환

1) I = 1

| 주소 | 마이크로-연산 필드 | 조건 필드(CD) | 분기 필드(BR) | 주소 필드(ADF) |

| 1 0001 00 | 000 000 | 01 | 01 | 000 0100 |

| 간접 사이클 루틴 시작 | ||||

| 000 0100 | 010 000 | 00 | 00 | 000 0101 |

| 000 0101 | 100 000 | 00 | 00 | 000 0110 |

| 000 0110 | 110 000 | 00 | 10 | 1 0001 01 (간접 사이클에서 LOAD 실행 사이클로 복귀) |

| 간접 사이클 루틴으로부터 복귀 | ||||

| 1 0001 01 | 010 000 | 00 | 00 | 1 0001 10 |

| 1 0001 10 | 100 000 | 00 | 00 | 1 0001 11 |

| 1 0001 11 | 101 000 | 00 | 00 | 000 0000 (인출 사이클 루틴으로 복귀) |

2) I = 0

| 주소 | 마이크로-연산 필드 | 조건 필드(CD) | 분기 필드(BR) | 주소 필드(ADF) |

| 1 0001 00 | 000 000 | 01 | 01 | 1 0001 01 |

| 1 0001 01 | 010 000 | 00 | 00 | 1 0001 10 |

| 1 0001 10 | 100 000 | 00 | 00 | 1 0001 11 |

| 1 0001 11 | 101 000 | 00 | 00 | 000 0000 (인출 사이클 루틴으로 복귀) |

STORE(I)

t(0) : IR(addr) -> MAR

t(1) : AC -> MBR

t(2) : MBR -> M[MAR]| ORG 72 (시작 주소 72) |

| 연산 기호 | 조건 기호 | 분기 기호 | 분기 목적지 | 설명 | |

| STORE(I): | NOP | I | CALL | INDRT | ; I=1 : 간접 사이클 루틴 호출 |

| IRTAR | U | JMP | NEXT | ; IR(addr) -> MAR ; 다음 마이크로명령어 실행 |

|

| ACTBR | U | JMP | NEXT | ; AC -> MBR ; 다음 마이크로명령어 실행 |

|

| WRITE | U | JMP | FETCH | ; MBR -> M[MAR] ; 인출 사이클 루틴으로 복귀 |

>> 마이크로명령어들을 2진 비트 패턴으로 변환

1) I=1

| 주소 | 마이크로-연산 필드 | 조건 필드(CD) | 분기 필드(BR) | 주소 필드(ADF) |

| 1 0010 00 | 000 000 | 01 | 01 | 000 0100 |

| 간접 사이클 루틴 시작 | ||||

| 000 0100 | 010 000 | 00 | 00 | 000 0101 |

| 000 0101 | 100 000 | 00 | 00 | 000 0110 |

| 000 0100 | 110 000 | 00 | 10 | 1 0010 01 (간접 사이클에서 STORE 실행 사이클로 복귀) |

| 간접 사이클 루틴으로부터 복귀 | ||||

| 1 0010 01 | 010 000 | 00 | 00 | 1 0010 10 |

| 1 0010 10 | 000 010 | 00 | 00 | 1 0010 11 |

| 1 0010 11 | 111 000 | 00 | 00 | 000 0000 (인출 사이클 루틴으로 복귀) |

2) I=0

| 주소 | 마이크로-연산 필드 | 조건 필드(CD) | 분기 필드(BR) | 주소 필드(ADF) |

| 1 0010 00 | 000 000 | 01 | 01 | 1 0010 01 |

| 1 0010 01 | 010 000 | 00 | 00 | 1 0010 10 |

| 1 0010 10 | 000 010 | 00 | 00 | 1 0010 11 |

| 1 0010 11 | 111 000 | 00 | 00 | 000 0000 (인출 사이클 루틴으로 복귀) |

ADD

t(0) : IR(addr) -> MAR

t(1) : M[MAR] -> MBR

t(2) : AC + MBR -> AC| ORG 76 (시작 주소 76) |

| 연산 기호 | 조건 기호 | 분기 기호 | 분기 목적지 | 설명 | |

| ADD: | IRTAR | U | JMP | NEXT | ; IR(addr) ->MAR ; 다음 마이크로명령어 실행 |

| READ | U | JMP | NEXT | ; M[MAR] -> MBR ; 다음 마이크로명령어 실행 |

|

| ADD | U | JMP | FETCH | ; AC + MBR -> AC ; 인출 사이클 루틴으로 복귀 |

>> 마이크로명령어들을 2진 비트 패턴으로 변환

| 주소 | 마이크로-연산 필드 | 조건 필드(CD) | 분기 필드(BR) | 주소 필드(ADF) |

| 1 0011 00 | 010 000 | 00 | 00 | 1 0011 01 |

| 1 0011 01 | 100 000 | 00 | 00 | 1 0011 10 |

| 1 0011 10 | 011 000 | 00 | 00 | 000 0000 (인출 사이클 루틴으로 복귀) |

SUB

t(0) : IR(addr) -> MAR

t(1) : M[MAR] -> MBR

t(2) : AC - MBR -> AC| ORG 80 (시작 주소 80) |

| 연산 기호 | 조건 기호 | 분기 기호 | 분기 목적지 | 설명 | |

| SUB: | IRTAR | U | JMP | NEXT | ; IR(addr) -> MAR ; 다음 마이크로명령어 실행 |

| READ | U | JMP | NEXT | ; M[MAR] -> MBR ; 다음 마이크로명령어 실행 |

|

| SUB | U | JMP | FETCH | ; AC - MBR -> AC ; 인출 사이클 루틴으로 복귀 |

>> 마이크로명령어들을 2진 비트 패턴으로 변환

| 주소 | 마이크로-연산 필드 | 조건 필드(CD) | 분기 필드(BR) | 주소 필드(ADF) |

| 1 0100 00 | 010 000 | 00 | 00 | 1 0100 01 |

| 1 0100 01 | 100 000 | 00 | 00 | 1 0100 10 |

| 1 0100 10 | 000 110 | 00 | 00 | 000 0000 (인출 사이클 루틴으로 복귀) |

JUMP

t(0) : IR(addr) -> PC| ORG 84 (시작 주소 84) |

| 연산 기호 | 조건 기호 | 분기 기호 | 분기 목적지 | 설명 | |

| JUMP: | IRTPC | U | JMP | FETCH | ; IR(addr) -> PC ; 인출 사이클 루틴으로 복귀 |

>> 마이크로명령어들을 2진 비트 패턴으로 변환

| 주소 | 마이크로-연산 필드 | 조건 필드(CD) | 분기 필드(BR) | 주소 필드(ADF) |

| 1 0101 00 | 000 111 | 00 | 00 | 000 0000 (인출 사이클 루틴으로 복귀) |

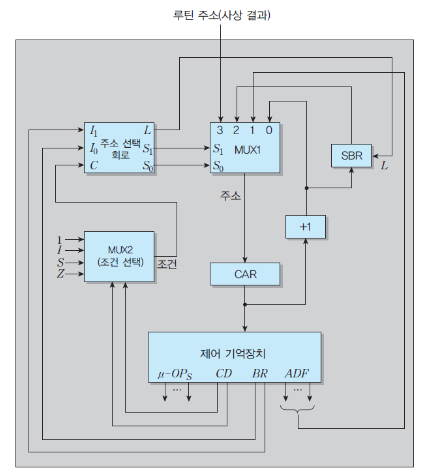

마이크로프로그램의 순서제어

- 순서제어 (Sequencing) : 다음에 실행할 마이크로명령어의 주소 결정

- CAR 초기값 : 0

- MUX1 : 다음에 실행할 마이크로명령어의 주소 선택

- MUX2 : 조건 플래그를 선택해서 주소선택 회로로 전송

주소 선택 방법

- BR = 분기필드

▶ BR = 00 (JUMP) or BR = 01 (CALL)

C = 0

- 다음 위치의 마이크로명령어 선택

C = 1

- 조건 필드가 1(분기 O)일 경우, ADF가 지정하는 위치로 JUMP or CALL

- CALL 하면, CAR 내용을 SBR에 저장

▶ BR = 10 (RET)

- SBR 내용을 CAR에 저장 :: 복귀

▶ BR = 11 (MAP)

- 사상 결과를 CAR에 저장

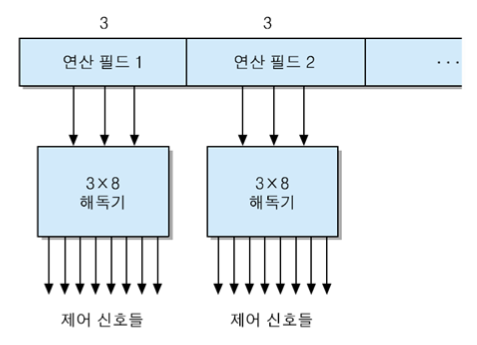

수직적 마이크로프로그래밍

- 마이크로명령어의 opcode에 encoded bits를 포함시킨다

- 해독기를 통해서 그 bit들이 필요한 수 만큼의 제어 신호들로 확장하는 방식

장점

- 마이크로명령어의 길이(bit 수) 최소화

- 제어 기억장치 용량 감소

단점

- 해독 동작에 걸리는 만큼의 지연시간 발생

- 연산 필드가 n비트라면

- 해독기를 통해서 최대 2n개 제어 신호들을 발생시킬 수 있다

수평적 마이크로프로그래밍

- 연산 필드의 각 비트와 제어신호를 1:1로 대응시키는 방식

- 필요한 제어 신호 수만큼의 비트드로 이루어진 opcode bit들이 마이크로명령어에 포함되어야 한다

장점

- 하드웨어가 간단하고, 해독에 따른 지연 시간이 없다

- 추가적인 하드웨어(해독기)가 필요없다

단점

- 마이크로명령어의 비트 수가 길어지기 때문에 제어 기억장치 용량이 증가한다