[컴퓨터구조] 시스템의 구성

시스템 버스 (System Bus)

- 컴퓨터의 구성요소(CPU, 기억장치, I/O장치)들을 서로 연결하고, Data/신호 교환을 위한 통로

- 한 번에 한 개의 장치만 Data 전송 가능

- 데이터 버스 / 주소 버스 / 제어 버스가 존재한다

데이터 버스 (Data Bus)

CPU와 (기억장치, I/O장치) 사이에서 Data를 전달하는 통로

- (기억장치, I/O장치)의 명령어와 Data를 CPU로 보낸다

- CPU 연산결과를 (기억장치, I/O장치)로 보낸다

- 데이터를 주고 받아야 하기 때문에 양방향 버스

- 데이터 버스 크기(폭) = 한 번에 전송될 수 있는 Data의 크기(비트 수)를 결정

- Word 크기, 레지스터 크기와 같다

- if 데이터 버스 크기 = 32bit >> Data를 한 번에 32bit씩 읽을 수 있다

주소 버스 (Address Bus)

CPU → (주기억장치, I/O장치)로 (기억장치 주소, I/O 장치 포트 번호)를 전달하는 통로

- Data를 정확하게 보내려면 주소가 필요하다

- 주소를 전달만 하기 때문에 단방향 버스

- 주소 버스 크기(폭) = 최대 기억장치 용량 결정 (2주소 버스 크기)

제어 버스 (Control Bus)

데이터버스, 주소버스를 제어하기 위해 제어신호들을 전송하는 통로

- 읽기/쓰기 동작을 모두 수행하기 때문에 양방향 버스

- CPU or 시스템 구성에 따라 제어 선 개수가 다르다

기억장치 읽기 신호

- 주소가 지정하는 기억장소의 Data를 읽고, 버스에 해당 Data를 실리게 하는 제어 신호

기억장치 쓰기 신호

- 버스에 실린 Data를, 주소가 지정하는 기억장소에 저장하게 하는 제어 신호

I/O 읽기 신호

- 지정된 I/O 장치로부터 Data를 읽어서, 버스에 해당 Data를 실리게 하는 제어 신호

I/O 쓰기 신호

- 버스에 실린 Data를, 지정된 I/O 장치로 출력하게 하는 제어 신호

CPU ↔ 기억장치 통신

액세스

- CPU가 Data를 기억장치에 저장하거나, 이미 저장되어 있는 Data를 읽는 동작

- 버스(주소, 데이터), 제어신호(기억장치 읽기/쓰기 신호)가 필요

적재(Load), 저장(Store) 명령에 의해 수행

▶ 적재(Load) : 기억장치 읽기

- 주소 버스 : 기억장치에서 읽을 Data가 저장된 주소값 전달 (CPU → 기억장치)

- 제어 버스 : "기억장치 읽기 신호" 전달 (CPU → 기억장치)

- 데이터 버스 : 해당 기억장치에 저장된 Data 전달 (기억장치 → CPU)

▶ 저장(Store) : 기억장치 쓰기

- 주소 버스 : Data를 저장할 기억장치의 주소값 전달 (CPU → 기억장치)

- 제어 버스 : "기억장치 쓰기 신호" 전달 (CPU → 기억장치)

- 데이터 버스 : 저장할 Data를 기억장치에 전달 (CPU → 기억장치)

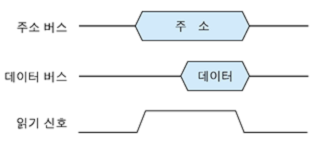

기억장치 읽기 동작 시간 흐름도

1. Data가 저장되어 있는 기억장치 주소를 주소버스를 통해 보내면서 '읽기 신호 활성화'

2. 지연 시간이 경과하고, 해당 기억장치의 Data가 데이터 버스에 실린다

※ 지연 시간

- 주소 해독 시간 + 기억장치로부터 Data 읽는데 걸리는 시간

>> 읽기 시간 : CPU가 기억장치로 주소를 보낸 순간 ~ 읽기 동작이 완료될 때까지 걸린 시간

기억장치 쓰기 동작 시간 흐름도

- (저장할 Data, Data를 저장할 기억장치의 주소)를 각각 (데이터버스, 주소버스)를 통해 보내면서 '쓰기 신호 활성화'

>> 쓰기 시간 : CPU가 기억장치로 Data/주소를 보낸 순간 ~ 쓰기 동작 완료될 때까지 걸린 시간

CPU ↔ I/O장치 통신

- 버스(주소, 데이터), 제어신호(I/O 읽기/쓰기 신호)가 필요

- 시스템 버스에서 I/O장치에 직접 연결하지 못하기 때문에 I/O 장치 제어기를 통해서 제어를 전달

- 접속 경로 : CPU ↔ 시스템 버스 ↔ I/O 장치 제어기 ↔ I/O 장치

입력(Input), 출력(Output) 명령에 의해 수행

▶ 입력(Input) : I/O 읽기

- 주소 버스 : I/O 장치 포트 번호 전달 (CPU → 기억장치)

- 제어 버스 : "I/O 읽기 신호" 전달 (CPU → 기억장치)

- 데이터 버스 : 해당 I/O 장치에 저장된 Data 전달 (기억장치 → CPU)

▶ 출력(Output) : I/O 쓰기

- 주소 버스 : I/O 장치 포트 번호 전달 (CPU → 기억장치)

- 제어 버스 : "I/O 쓰기 신호" 전달 (CPU → 기억장치)

- 데이터 버스 : 저장할 Data를 I/O 장치에 전달 (CPU → 기억장치)

인터럽트 (Interrupt)

- I/O 장치는 제어신호를 통해서 인터럽트 요청을 보내서 CPU한테 I/O작업을 요청할 수 있다

※ 인터럽트 요청 (I/O → CPU)

- I/O 준비를 끝낸 I/O 장치가 CPU한테 I/O 작업 요청

※ 인터럽트 확인 (CPU → I/O)

- CPU가 I/O 작업을 수행하는 것을 I/O 장치에 통보

I/O 장치 제어기 레지스터

- 상태 R / 데이터 R 각각에 주소가 할당된다

- I/O 장치에는 기본적으로 2개의 주소가 할당

※ 데이터 레지스터

- CPU ↔ I/O 장치 간에 전달되는 Data들을 일시적으로 저장

- Data 임시 기억 장치

※ 상태 레지스터

- I/O 장치의 현재 상태를 나타내는 비트들을 저장하는 레지스터

- 준비 상태(RDY), 데이터 전송 확인(ACK) 비트,... 등이 존재한다

기억장치 ↔ I/O장치 통신

- CPU를 이용하지 않고, 직접 기억장치 엑세스 방식 (DMA : Direct Memory Access)으로 통신

- DMA 제어기는 CPU를 대신해서 주소버스, 제어버스에 신호 전달

- DMA 제어기는 통신 시작 전에 CPU한테 버스 사용 허가를 받아야 한다